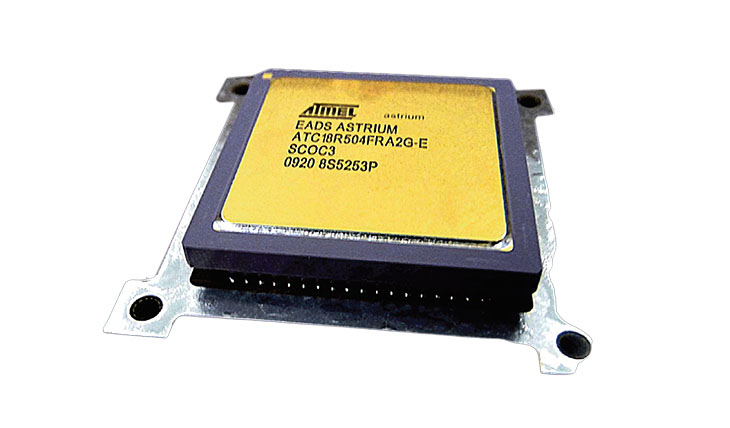

SCOC3

Overview

The SCOC3 ASIC was designed to fulfill 2 major objectives: (1) to take benefit of the latest electronic integration and miniaturization technologies to reduce mass and cost of space computers, (2) to propose a European universal computer core as a building block for any satellite platform, extendable to payload computers.

The LEON3FT Sparc V8 32 bits processor IP has been integrated with standard interface IP used on satellite - SpaceWire, 1553, CAN, UART - and with state of the art utilities for processor such as floating point unit, Memory Management Unit, large caches, debug function, memory controller.

CCSDS standard TM/TC control is included in the ASIC. This allows one board to be eliminated with respect to the former platform computer generation. The ASIC is implemented using the largest matrices of the ATMEL ATC18RHA technology: 3.6 Mgates at 180 nm on a 170 mm2 Si chip. The packaging is a MCGA 472, offering 342 IO for users over a small surface.

Looking for more information or want to purchase?

Overview

- Name

- SCOC3

- Vendor

- Airbus

- Subsystem

- CDH Subsystem

- Component Type

- Processor

- Form Factor

- All

- Heritage

- N/A

Vendor Details

- Name

- Airbus

- Website

- https://www.airbus.com/

- Founded

- 1970

Vendor Request for Information Form

Specifications

- Subsystem

- CDH Subsystem

- Component Type

- Processor

- Form Factor

- All

- Vendor

- Airbus

- Dry Mass

- 0.012 kg

- Average Power

- 1.0 W

- Heritage

- N/A

- Status

- In Production

Try Designer

Design, model, and evaluate satellite mission concepts quickly with our software.

Airbus

View all products